The deployment of mega-constellations and small sats and their new usage model based on reconfigurability on the fly during the life of the vehicle is driving a change in how they are designed.

In this 3-part series, we will look at how adaptive configurability using programmable SoC’s becomes the tool of choice in the repertoire of system designers to speed up design and qualification of LEO satellites:

Evolution of Control Systems in Satellites

The current systems using discrete solutions for common measurement and control applications or small FPGA/ASIC solutions for real time applications that are cumbersome and vulnerable to failure can now be replaced by a singular, highly configurable SoC.

Avalanche’s Space Grade SoC Architecture

How a single programmable SoC can replace numerous functions and offer a “future proof” design capable of in-orbit upgrade and optimized SWAP-C (size, weight, power and cost).

SWAP-C Optimization Made Possible by Blizzard RT-SoC

Not only does the board-level Size, Weight, Power and Cost (SWAP-C) profile improve by using Avalanche’s Blizzard SoC, system designers can also appreciate the benefits of overall system level reuse of a cost effective, flexible SoC platform, with implications to design, test, qualification and more scalable capability in flight.

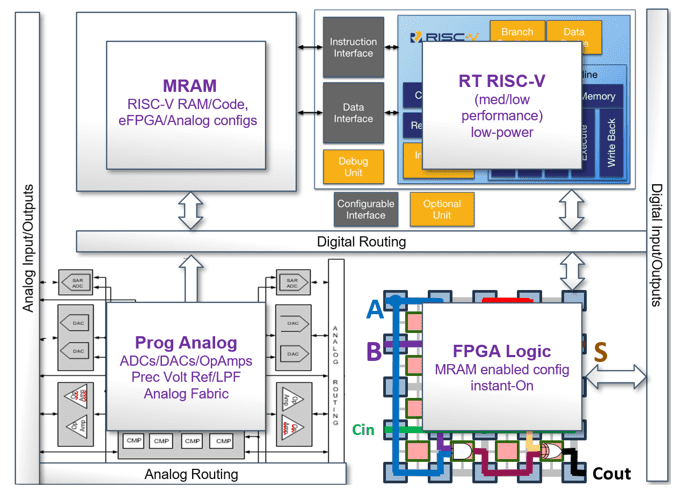

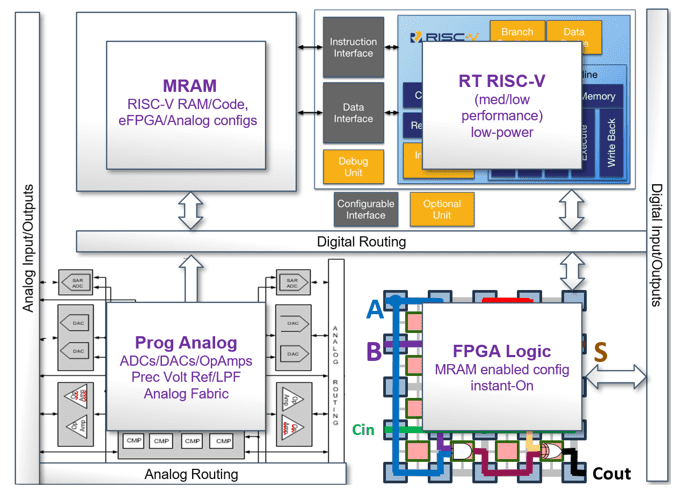

We will now shift toward a more detailed view of Avalanche Technology’s novel Radiation Tolerant (RT) SoC architecture, walking through each of the key functional blocks depicted below in Figure 1 and how they support the evolution of NewSpace satellite infrastructure. We further showcase how the integration and flexibility of a single component can replace numerous functions and offer a “future proof” design capable of in-orbit upgrades and optimized SWAP-C (size, weight, power and cost). We will touch upon the generational rollout of this novel SoC family which can accelerate module, subsystem, system, and vehicle from design through to qualification, manufacturing and Integration & Test (I&T) for improved Time-To-Market.

Figure 1: Key functional blocks in the Blizzard RT-SoC

As mentioned in the prior blog in this series, the key functional blocks of the Blizzard RT-SoC architecture include a 40 MHz RISC-V processor (with 2kB of on-chip SRAM), embedded FPGA functionality, programmable analog, and non-volatile memory (external for the first generation). At the heart of this architecture, the PicoRV-based CPU is a general purpose, low power, flexible standard processing platform that can configure and monitor each subsystem board, yet powerful enough to handle the power distribution management functions. We aren’t that far removed from the days where a RAD6000, RAD750, or RHPPC603e were the only options satellite designers had to run the entire satellite as well as manage and process the data from various payloads. With the advent of small satellites and distributed system architectures, our RT SoC processor is more than sufficient to manage the Power Distribution Unit and avionics for a typical modern satellite. It can also handle control and processing functions for each module, including command & control, telemetry, and payload modules to enable more robust and efficient board-level integration and test by virtue of personalization and design reuse. Subsequent generations will offer beefier processor performance for additional edge processing optionality.

From the programmable analog functional block of the RT-SoC you have a very capable low power 8-bit 1MSPS SAR ADC as well as an 8-bit DAC with similar performance, ideal for monitoring state-of-the-health as well as actuator control. These data converters along with some additional programmable analog functions in the RT-SoC allow standardized modules to contain their own telemetry and only pass key digital data to the system processor rather than having everything routed through connectors to a dedicated board or box for monitoring and management. Whether it’s passing this data via the UART, SPI or the CAN-FD interface, the RT-SoC offers the flexibility to communicate with heritage interfaces as well as emerging new standards for more seamless integration and scalability. The 39-software configurable GPIOs also allow the RT SoC to handle routine system management, monitoring and maintenance functions, ensuring the satellite is performing at optimal health and performance. Over the course of RT-SoC generational evolution, these programmable analog functions will be expanded in number and capability.

The digital embedded FPGA fabric, while only 64 CLBs in the first generation, can support various glue logic functions allowing the larger more powerful FPGAs to focus on processing the converged data streams from the growing sensor networks. The RT SoC digital fabric can also enable better segmentation of critical satellite functional modules such as power, telemetry, safety monitoring, propulsion control, and antenna pointing modules without having to burden the larger FPGA or processor or add risk. As these larger FPGAs often undergo continuous changes with new payloads and functions coming online, it becomes difficult to ensure critical command and control functions have not been compromised without being self-contained as they are in the RT-SoC. This embedded FPGA fabric will grow in size and capability over the course of subsequent RT-SoC generations to bolster edge processing capability.

The STT-MRAM section is external for the first generation SoC but is then integrated for optimal scalability. This high-reliability non-volatile Space Grade memory technology at the heart of Avalanche Technology’s product offering provides the ideal blend of radiation resilience, high density, endurance and speed for viable unified memory candidacy. While standalone memory device densities will see 16Gb in 2022, the Gen 2 RT-SoC will embed 16Mb, providing the ability to store the processor’s boot image along with several personalization options for the digital fabric and still has enough room for critical scratch pad data and tables for each of the modules while communicating with the rest of the systems. Densities will scale on future generations, to match the enhanced capabilities of the other system blocks.

This combination of capabilities provides a backbone for device and system level configurability while standardizing around a singular hardware framework for centralized testing & qualification, economies of scale and situational personalization. Each of the functional blocks outlined can be used in standalone modes or combined according to program needs and offer a cost-effective processing architecture that can be sprinkled around a satellite system design. In the final chapter of this RT-SoC blog series, we will dig more deeply into how the unique Blizzard RT-SoC architecture can enable SWAP-C reduction in common satellite architectures, examining specific before and after use cases.